RISC Processor

- Project Type: Hardware Model

- Languages: SystemVerilog

- Tech Stack: Modelsim, Quartus Prime Synthesizer, De1-Soc FPGA

- Project Links: GitHub

Project Details

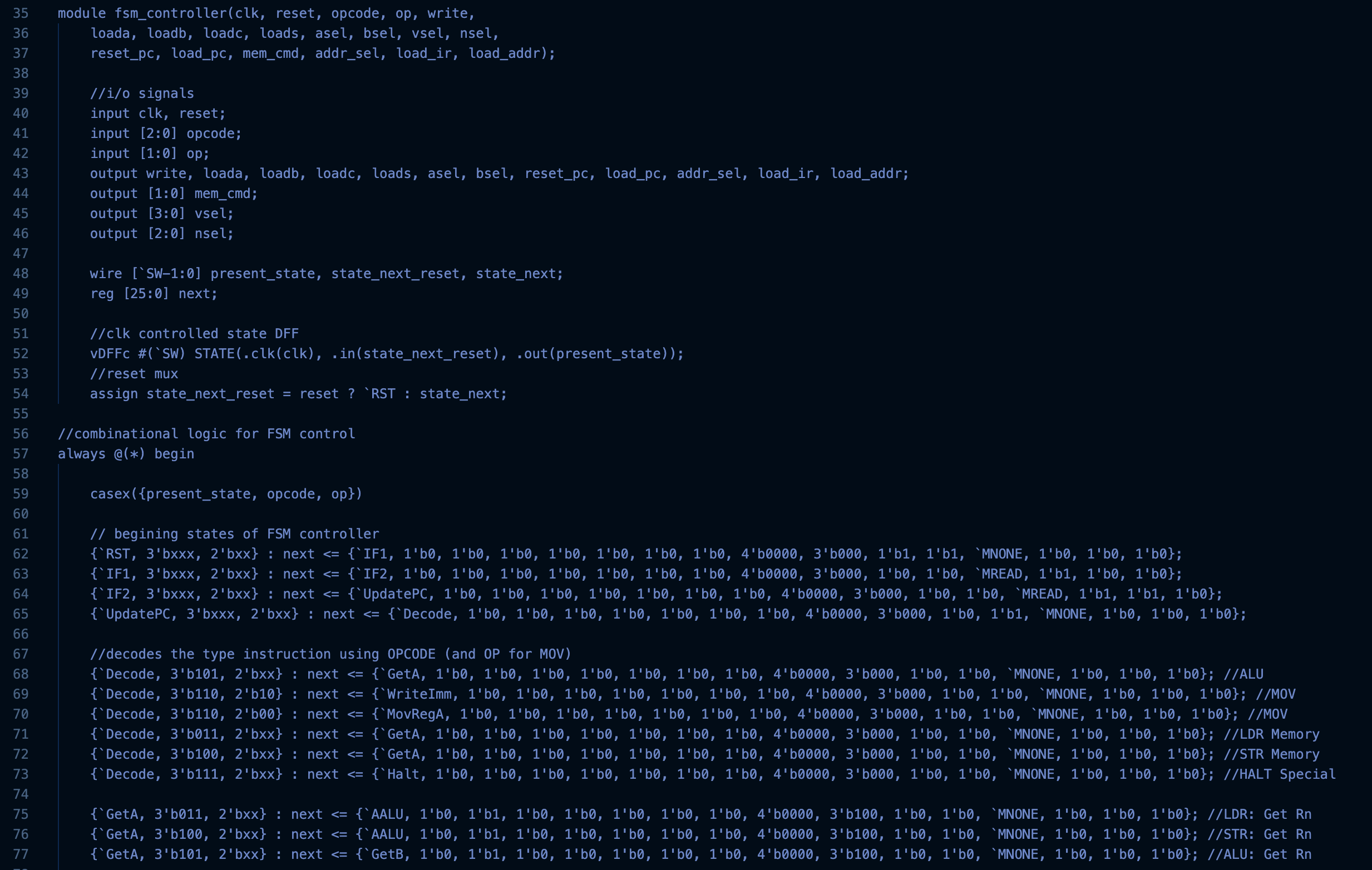

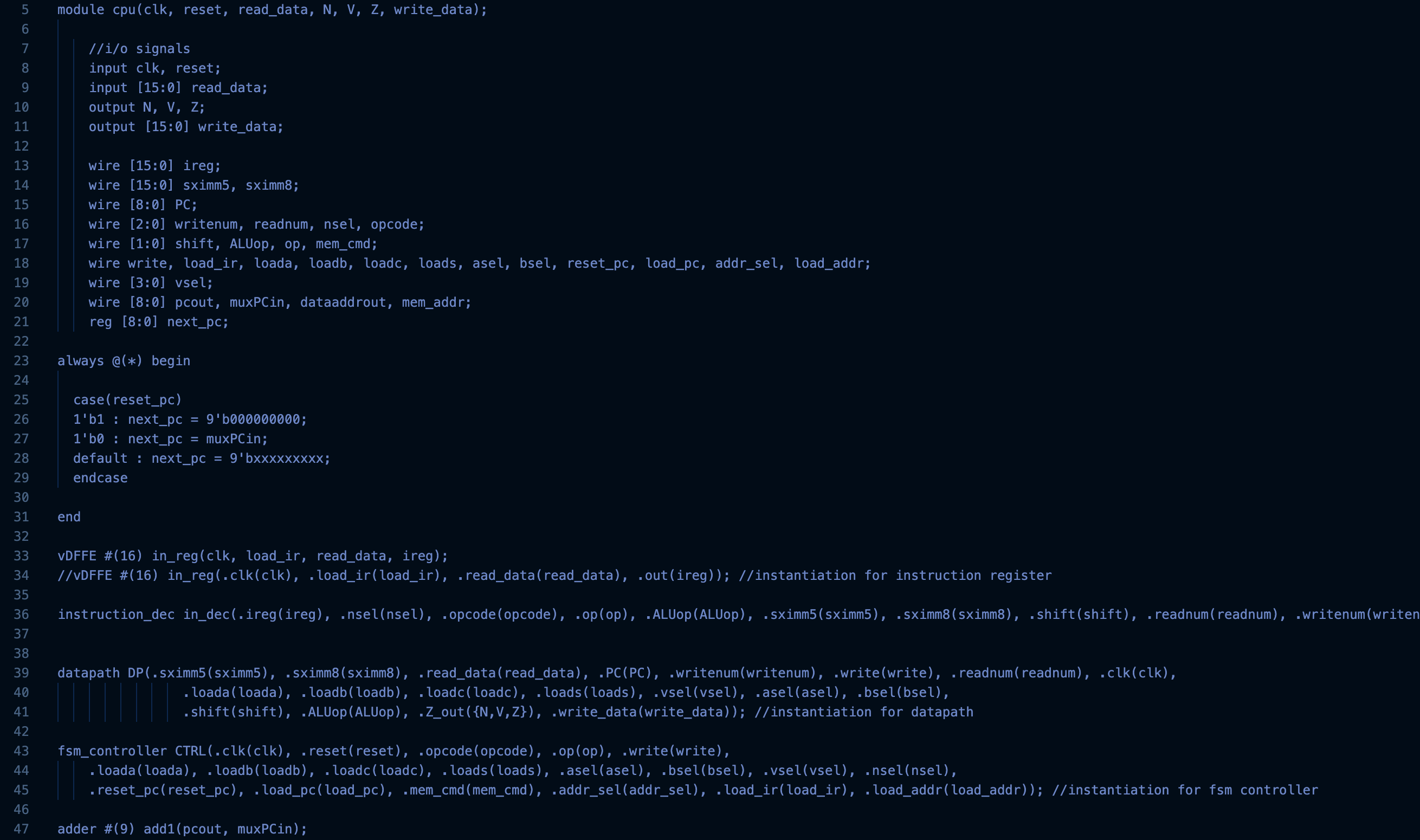

This project includes various iterations of a finalized Reduced Instruction Set Computer (RISC). The early stages focus on the building blocks of using Verilog and utilizing the capabilities of a Finite State Machine (FSM). Next is the first complex application of Verilog to design a functionally limited RISC machine. It includes a top-level module that instantiates a computer datapath that works to connect a variety of smaller components, each of which completes more trivial tasks. In its entirety, it can use specifically provided input to compute and display the desired output. From there, I began to extend the versatility of the previous iteration by working to integrate a complex FSM, similar to the one experimented on earlier. The FSM allows for a broader range of inputs and outputs as well as automating the whole process. With this design, the RISC machine can function independently and return the desired output with fewer steps and potential SPOFs. The last stage focuses on implementing memory into the design. This would enable it to act more like a real-world processor, as it can recall and save information for later instances, and again simplify the I/O process for a user. In addition, it implements associated commands that allow a user to store and read information to and from a desired location within the computer. Altogether, this iteration outlines a functioning and detailed RISC Processor.